一天速成,数电还是过于简单。

数电学习笔记

我会的东西都没记。

第一章

1.1数字信号

什么是模拟信号?什么是数字信号?

模拟信号在时间上是连续的,数字信号是离散的

数字信号的优势:

- 抗干扰能力强,只有高低电平。

- 功耗比较低。数字电路不需要能量的放大。

1.2数制

skipskip

第二章

2.1逻辑问题的描述方法

介绍简单的与或非 skip

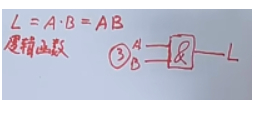

与:\(L=A*B\)

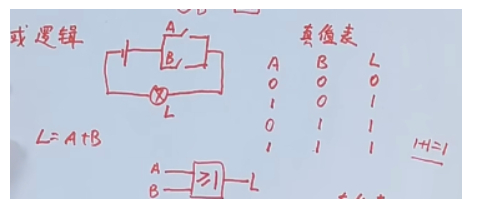

或:\(L=A+B\)

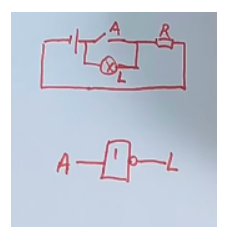

非:\(L= \overline{A}\)

异或:\(L= \overline{A}B+A\overline{B}\)

同或:\(L= AB+\overline{AB}\)

2.2逻辑函数的表示方法

-

0-1律

\(A+0=A,A*0=0,\overline{0}=1\)

\(A+1=1,A*1=A,\overline{1}=0\)

-

幂等律

\(A+A=A , A*A=A\)

-

互补律

\(A+\overline{A}=1,A*\overline{A}=0,\overline{\overline{A}}=A\)

-

结合律

\((A+B)+C=A+(B+C) , (AB)C=A(BC)\)

-

交换律

\(A+B=B+A , AB+BA\)

-

分配律

\(A(B+C)=AB+AC\)

-

德摩根定理(与变或,或变与)

\(\overline{A*B*C*...}=\overline{A}+\overline{B}+\overline{C}+...\)

\(\overline{A+B+C+...}=\overline{A}*\overline{B}*\overline{C}*...\)

一些基本规则:

-

代入规则

可以把A,B代入其他逻辑式

-

反演规则

对于任意一个逻辑式Y,将其中所有的与换成非,所有的非换成与,,所有的1换成0,所有的0换成1,A换成\(\overline{A}\),\(\overline{A}\)换成A,B同理,可得 \(\overline{Y}\) 。

-

对偶规则

与反演规则一样,将其中所有的与换成非,所有的非换成与,,所有的1换成0,所有的0换成1。区别是没有改变A和B。经过变换后得到的表达式时L的对欧式,用 \(L'\) 表示。

若两逻辑式相等,它们的对偶式也相等,这就是对偶原理。

可以通过证明对偶式相等来证明逻辑式相等,有的时候会更加容易。

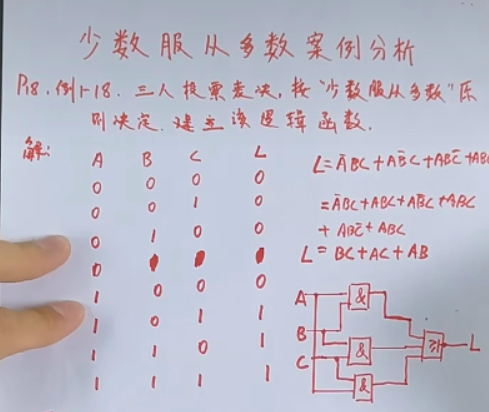

2.3 少数服从多数案例分析

思路:由

可在式中加入两个ABC,不影响式子的值。

2.4 最小项

-

最小项

-

定义:每个变量均以原变量或反变量的方式在该乘积项中出现一次

-

性质:

- 任意两个最小项,它们的乘积为0

- 全体最小项之和为1

- 每个最小项都对应固定的一组取值

-

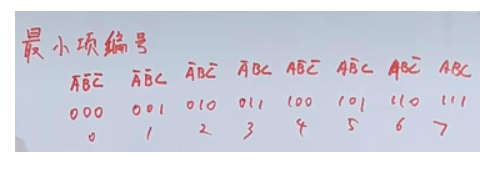

编号:

-

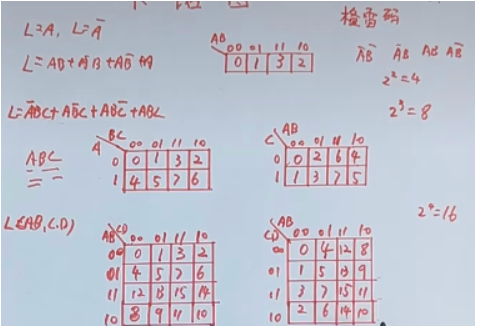

2.5 卡诺图

- 写上变量的名字,如AB

- 画小方格,需要 \(2^{n}\) 个

- 写格雷码

- 填最小项编号

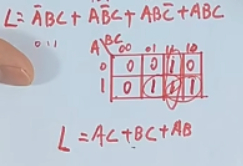

2.6卡诺图的化简

-

把乘积项在卡诺图中填入“1”,剩下的空格子写“0”

-

”画大饼“:

- 圈中有\(2^{n}\)个1

- 圈的数量较少,圈较大

- 每个1都被圈起来

- 1可以被重复使用

-

将每个圈中的项相“或”

-

再将所有圈的结果相“或”

第三章 逻辑门电路

3.1二极管组成的门电路

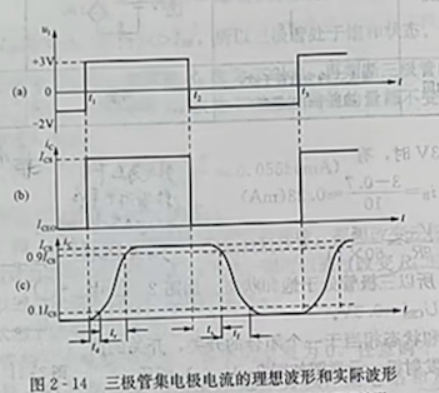

对于一个二极管,从截止到导通是瞬间完成的,但从导通到截止是需要一定时间的。

(开关损耗)

如果反向恢复时间大于电压反向的时间,就会出现二极管一直导通的情况。

也是由PN结组成的三极管同理:

不过普通的逻辑门电路的损耗很大,效率很低,玩不了3A游戏(

这暂时不在我们的考虑范围之内/

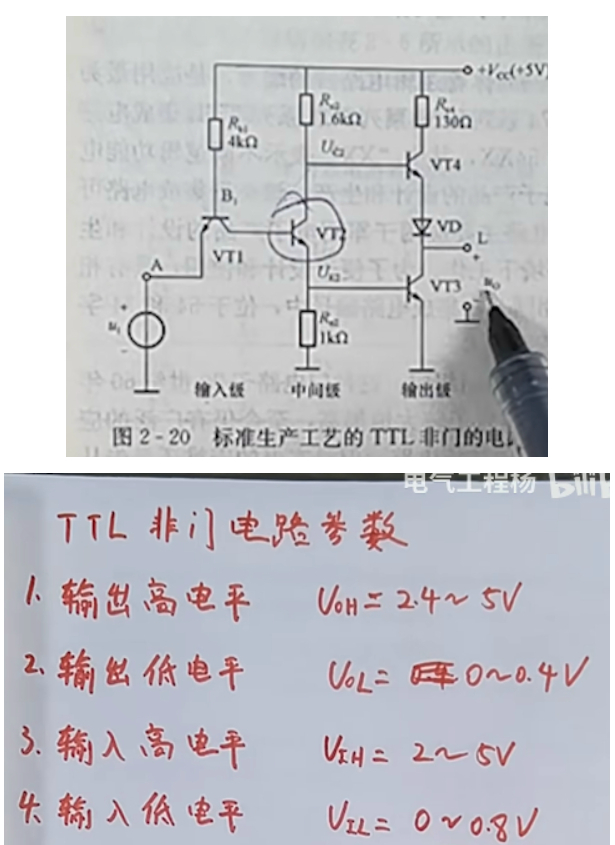

3.2TTL门电路

1. TTL非门

噪声容限电压:在级联时,输出高电平最低为2.4V,输入高电平最低为2V,存在2.4-2=0.4V的噪声容限电压(所能承受的最大干扰)。

2.扇出系数

- 最大输出低电平电流与输入低电平电流 \(I_{IL}\) 之比定义为输出低电平时的扇出系数,用 \(N_{OL}\) 表示,即能带动的同类负载门的个数(要舍掉小数部分取整数)。其表达式为:

- 最大输出高电平电流与输入高电平电流 \(I_{IH}\) 之比定义为输出高电平时的扇出系数,用 \(N_{OH}\) 表示,即能带动的同类负载门的个数(要舍掉小数部分取整数)。其表达式为:\[N_{OH}=\frac{I_{OH(max)}}{I_{IH}} \]

3.3组合逻辑电路的分析与设计

一、数字电路的分类

- 组合逻辑电路(L只与ABCD有关)

- 时序逻辑电路(L不只与ABCD有关,还与时间 t 有关)

二、组合逻辑电路的分析方法

分析顺序:文字描述——真值表——逻辑函数——逻辑电路

从左到右是组合逻辑电路的设计,从右到左是组合逻辑函数的分析

3.4竞争与冒险

以 \(L=A+\overline{A}\) 为例,非门的反应需要时间。这就导致A从1切换到0的瞬间,L的波形图会出现一个毛刺(原理同二极管)。(静态1冒险)

\(L=A*\overline{A}\) 是静态0冒险。

定义:

- 竞争:门电路两个输入信号同时向相反的逻辑电平跳变的现象称为竞争。

- 竞争-冒险:由于竞争而在电路输出端可能产生尖峰脉冲的现象。

如何判断一个逻辑函数是否存在冒险?

- 是否存在 \(A+\overline{A}\) 或 \(A*\overline{A}\)

五种消除竞争-冒险现象的方法

-

加冗余项

\(L=\overline{A}D+A\overline{C}=\overline{A}D+A\overline{C}+\overline{C}D\)

当D=1,C=0时,变为

\(\overline{A} +A+1=1\) ,就不存在静态1冒险了。

-

变换函数逻辑式,消去互补变量

-

增加选通脉冲

强制一个正电平

-

引入封锁脉冲

强制一个负电平

-

增加输出滤波电容

滤波,实践中比较实用

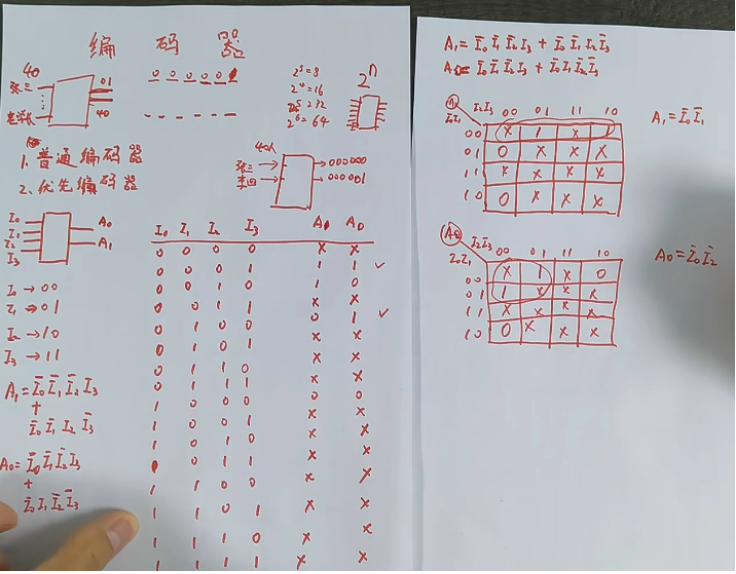

3.5 编码器基础

编码器的作用:将输入的每一个高、低电平信号编成一个对应的二进制代码

-

普通编码器

任何时刻只允许输入一个信号,否则会发生混乱

-

优先编码器

在同时输入多个信号的时候,优先编码器只会给优先级最高的信号编码

n位的编码器可以对 \(2^n\) 个信号进行编码

在计算机系统中,往往会以0作为有效信息

3.6 74X148编码器

小圆圈:低电平有效,非的意思

所以 \(I_{7}\) 的111的编码为000, \(I_{0}\) 的000编码为111

GS:区分芯片是否有电且有输入

EI:使能输入。

EI可以与上个芯片的EO相连,再把所有的输出端进行并联,一起接入与门。

高位权的EO连低位权的EI,完成编码器的扩展

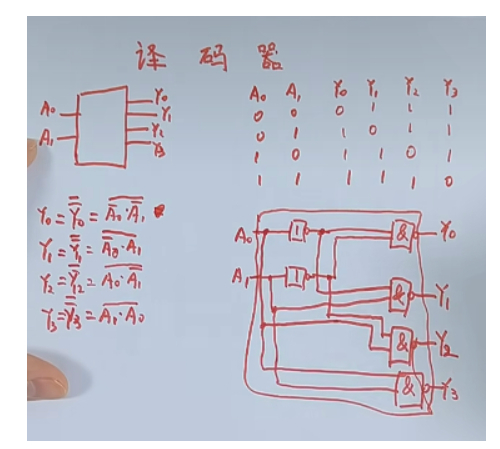

3.7 译码器

与编码器实行相反的操作,

作用是将每个输入的二进制代码译为输出高、低电平信号或者另外一个代码。

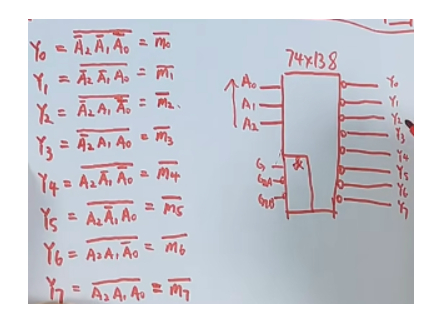

3.8 74X148 译码器

输出特性:(重点)

译码器的扩展

与编码器原理一致

二进制译码器可以作为数据分配器使用

3.9 数据选择器

-

特点:

有多个数据输入,只有一个数据输出(多对一)

-

区别:

数据分配器的特点:只有一个输入,但是有多对输出(一对多)

译码器的输出有八个,数据选择器的输出只有两个

-

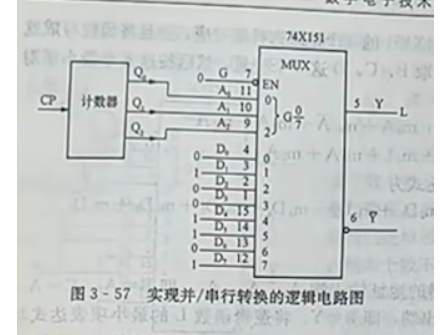

并行数据转串行数据:

通过加入计数器,可以将同一时刻接受到的并行数据通过计数器的控制,每个数据单独发出去

第四章 触发器

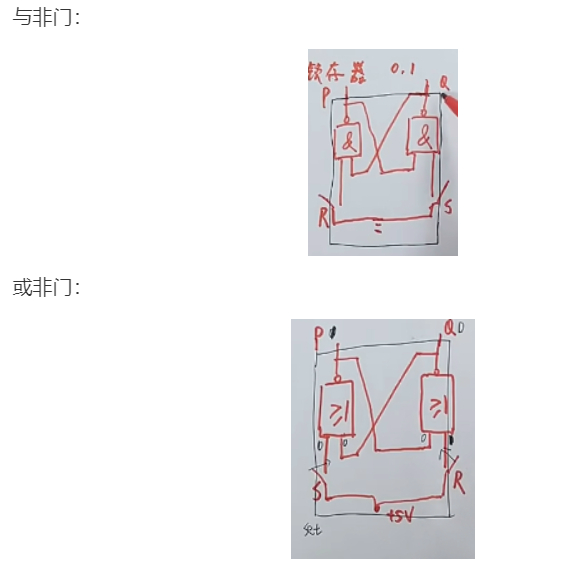

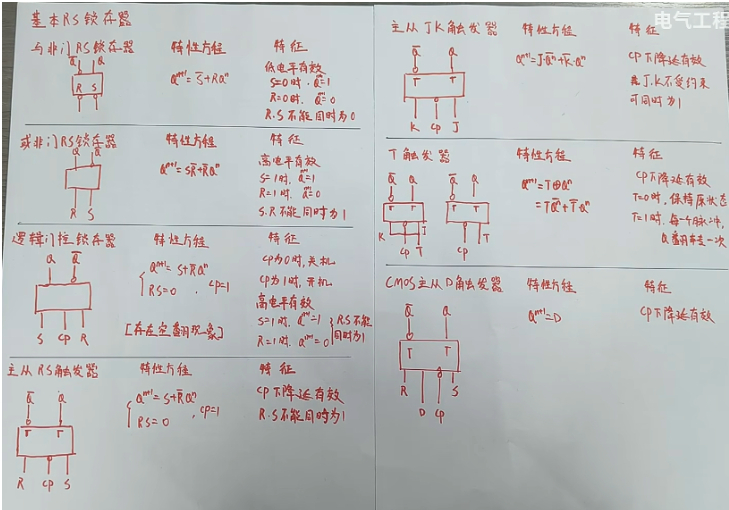

4.1 RS锁存器

由两个或非门/与非门首尾相连组成的电路。

若输出P满足 \(P=\overline{Q}\) ,那么此时锁存器就会认为当前存储的数据是有效的。

反之无效。

按下R,锁存器置0(Q=0,P=1)

按下S,锁存器置1(Q=1,P=0)

同时按下,P=Q=1,锁存器不正常工作

同时松开,P=Q=0,P=Q=0一直循环

(R,S不能同时为0)

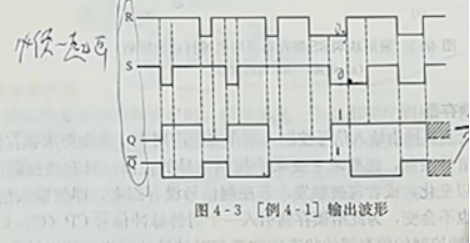

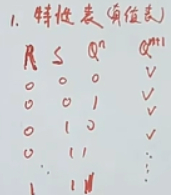

特性表(真值表plus):

逻辑函数:

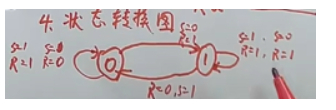

状态转换图:

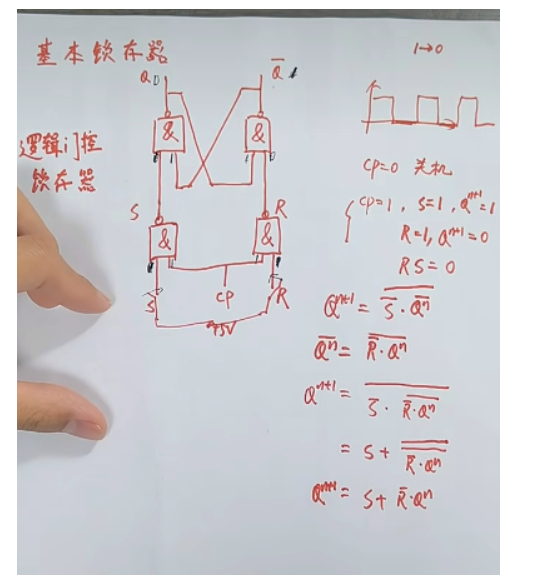

4.2 逻辑门控锁存器和JK触发器

逻辑门控锁存器

-

定义:在与非门锁存器的基础上,再用两个与非门和一个时钟cp进行S,R 的控制

-

特性:与或非门组成的锁存器相同

RS不能同时为1

-

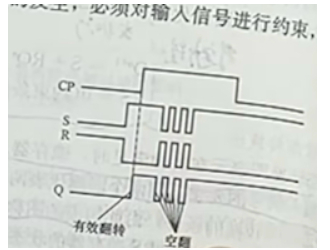

空翻现象:

举个例子,当 S 的输入信号为高电平,但由于受到干扰,信号不稳定,导致S会出现间断的低电位。这是Q的输出也会出现间断的低电位。

-

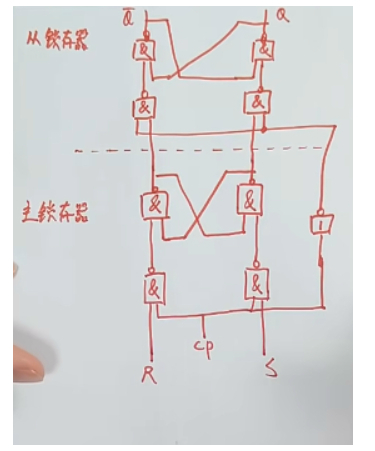

解决空翻现象的方法:主从触发器

实际上就是把两坨逻辑门控锁存器相连

CP=1的时候,主锁存器工作,从锁存器不工作。(输入数据)

CP=0的时候,从锁存器工作,主锁存器不工作。(输出数据)

前提:RS=0,在CP下降沿有效。

这样能有效地避免空翻现象

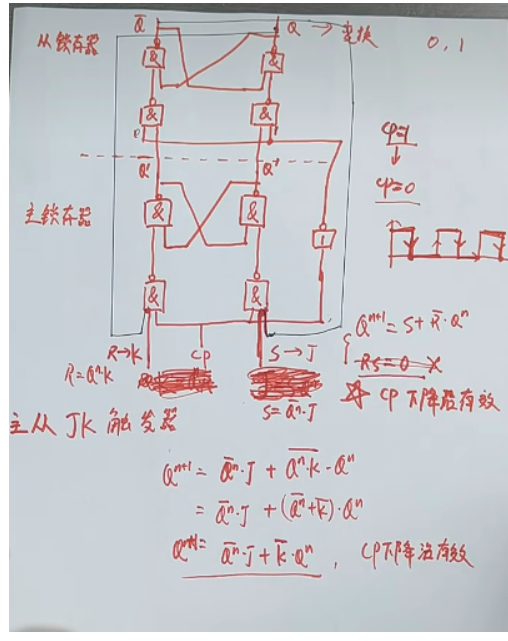

4.3 JK触发器

将主从触发器的输出 \(Q,\overline{Q}\) 分别接入 R,S 的与非门,由于 \(Q,\overline{Q}\) 中必有一个为0,那么 R,S 就算同时为1,在经过与非门只会也不会同时为0。

总结:

注意:CMOS触发器是上升沿有效,上面写错了。

第五章 时序逻辑电路

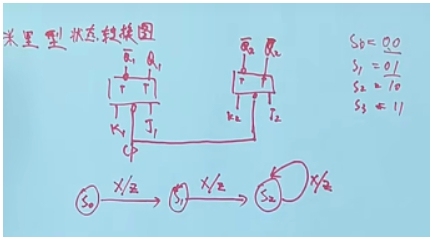

5.1 时序逻辑电路的描述

-

组成:

组合逻辑电路+存储电路

-

分析方法:

输出方程

\[Z=F(x,Q^n) \]驱动方程(激励方程)

\[D=F(x,Q^n) \]状态方程

\[Q^{n+1}=F(D,Q^n) \]电路——三个方程——总结出状态转换表——状态转换图——功能

-

分类:

第一种分类方法:

-

同步时序逻辑电路

触发器由同步时钟触发

-

异步时序逻辑电路(太难了,考试不怎么考)

触发器由异步时钟触发

第二种分类方法:

- 米里型

-

摩尔型

只受到存储电路现态的影响

-